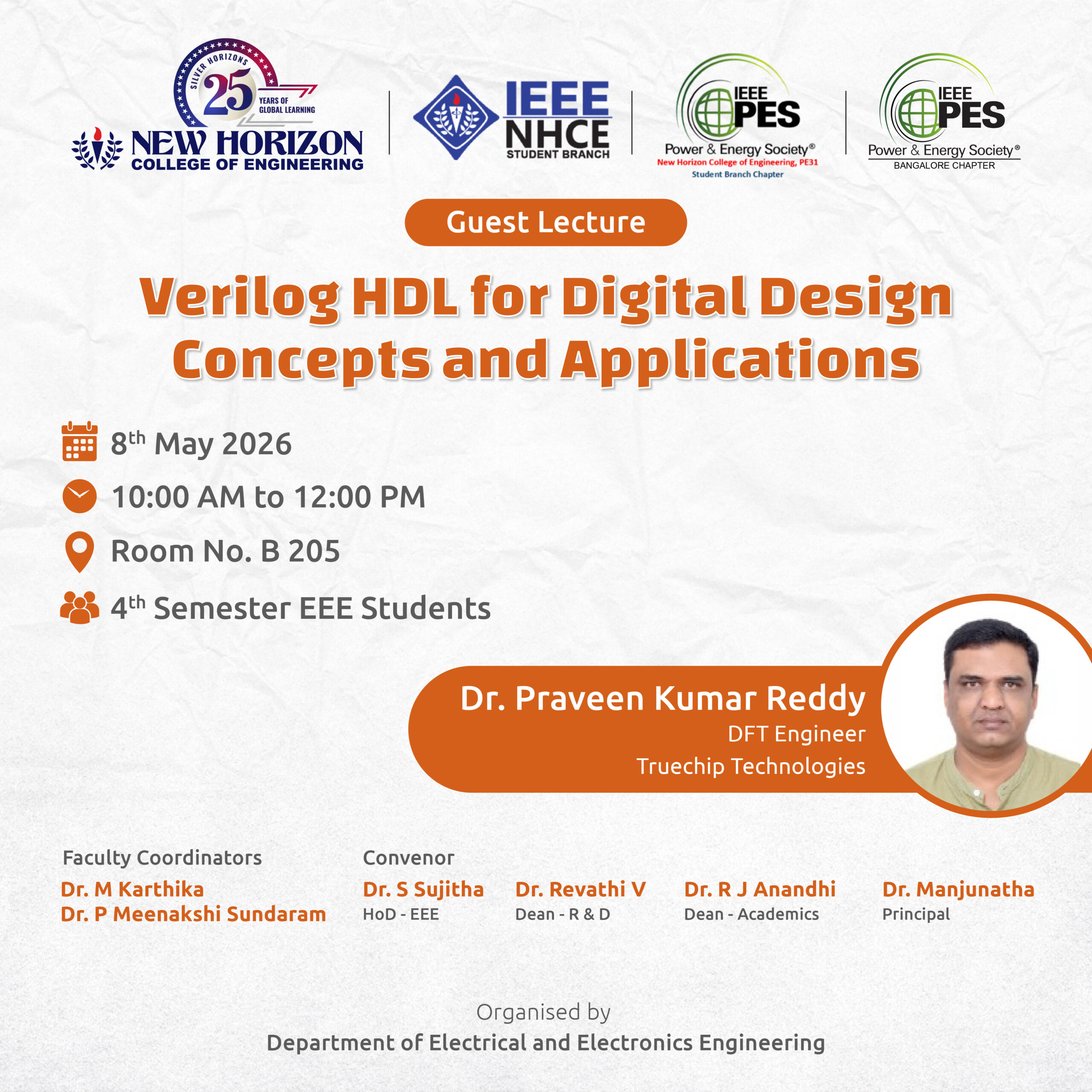

EVENTS

Verilog HDL for Digital Design

Concepts and Applications

Start Time

10:00 AM

May 08, 2026

Finish Time

12:00 PM

May 08, 2026

Event Info

Verilog HDL (Hardware Description Language) is an industry-standard language used to model, simulate, and synthesize digital circuits. It enables engineers to describe hardware behavior and structure at multiple abstraction levels — from gate level to behavioral.

Key areas typically covered: combinational & sequential logic design, FSMs, testbench writing, synthesis-ready coding styles, and real-world ASIC/FPGA applications.

Organising Team

| slno | Role | Name |

|---|---|---|

| 1 | Faculty Coordinator | Dr. M Karthika |

| 2 | Faculty Coordinator | Dr. P Meenakshi Sundaram |

| 3 | Convenor & HoD – EEE | Dr. S Sujitha |

| 4 | Dean – R&D | Dr. Revathi V |

| 5 | Dean – Academics | Dr. R J Anandhi |

| 6 | Principal | Dr. Manjunatha |